Új hozzászólás Aktív témák

-

S_x96x_S

őstag

>Honnan veszed, hogy "extrém minimális" lesz sok mag mellett?

>ezek pedig jelenleg a CCX<-IF->CCX kommunikációra vezethetőek vissza.64 magnál ugyanúgy megmaradnak a CCX-ek - nem lesz monolitikus design.

úgyanúgy kell kommunkálni.

A te javaslatoddal csak részben lett megoldva a probléma.

Viszont a többi fejlesztéssel ezt a problmát minimalizálni lehetett.A ZEN1 érzékeny volt a memórisebességére és a késleltésre. Ha ezt lecserélik és duplázzák az L3-at,

akkor a te általad jelzett ZEN1-es problémát minimalizálták.A mostani konkurenciával meg hiába hasnlítod össze. extrém magszám felett ők is ragasztóznak.

>Deszktopon ez úgy tűnik semennyire nem fog változni,

>ugyanúgy megmarad a <4-mag> <=IF=> <4-mag> rendszer

>mint potenciálisan szűk keresztmetszet kicsit javított késleltetésekkel.Az Intel monolitikus designjával ne hassonlítsd össze, főleg mert

az új Intel desing (dual-ring?) meg lehet, hogy másolja az AMD-t.

"

There is also some suggestion Intel might utilise a dual ring bus design for this Comet Lake chip, instead of the single ring bus used for the i9 9900K, or the mesh design picked up by the similarly ten-core i7 7900X and upcoming i9 9900X. That’s an intriguing thought and could possible suggest a move to something more akin to AMD’s CCX design.With this Comet Lake rumour that would potentially suggest a pair of either five- or six-core chips (with one core disabled) arrayed in a similar way to the quad-core CCX of Ryzen. And that sort of setup will need a whole lot of space.

"

https://www.pcgamesn.com/intel-comet-lake-cpu-10-core-14nmHa az Intel össze tud rendesen ragasztózni 2 chipletet - akkor az AMD-nek is képesnek kell lennie rá.

>Játékokban ez továbbra is vissza fog ütni.

meglátjuk mivel kompenzálja ezt az AMD. Ha lesz egy böszme nagy L4-es cache, akkor kevésbé lesz érzékeny a DDR4 memória sebességére , jobb lesz a játékoknál is.

és nem lehet annyira észrevenni mint most.Mottó: "A verseny jó!"

-

#95904256

törölt tag

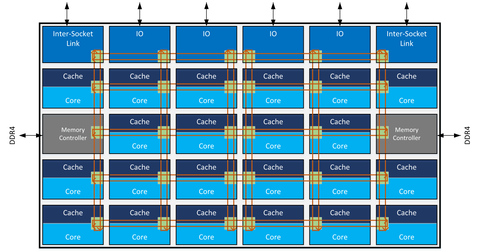

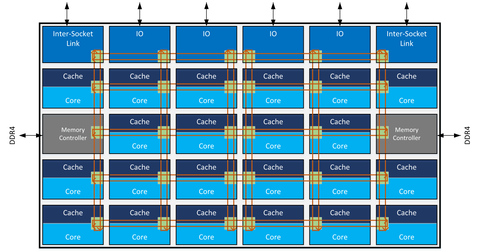

Nem egészen értem, hogy miért látod jelentős problémának, hogy csak 4 mag osztozik az L3-on és a többi magot csak buszon keresztül tudják elérni. Nézd meg pl. a sokmagos Intel szerverprocesszorok felépítését ( Skylake-SP ):

Itt minden mag a buszon csücsül a saját kis L3 cache darabkájával. Ők sem problémáztak rajta.[ Szerkesztve ]

Új hozzászólás Aktív témák

ph Gyorsítótárral brutálisan ki van tömve a Zen 2, 64 maggal majdnem 300 MB-ról beszélünk.

- sh4d0w: Darth Vader, a Lázadó

- Továbbra is roppant népszerű a Resident Evil 2 Remake

- OLED TV topic

- Ukrajnai háború

- Kerékpárosok, bringások ide!

- Formula-1

- Xiaomi 13T és 13T Pro - nincs tétlenkedés

- Bambu Lab X1/X1C, P1P-P1S és A1 mini tulajok

- Xbox tulajok OFF topicja

- BestBuy topik

- További aktív témák...