Új hozzászólás Aktív témák

-

Petykemano

veterán

válasz

S_x96x_S

#5243

üzenetére

S_x96x_S

#5243

üzenetére

A hősűrűség (thermal density) eddig is fokozódó problémát jelentett.

A hősűrűség azért jelent problémát, mert magas hőmérsékleten ugyannak a frekvenciának a tartásához magasabb feszültségre van szükség, ami növeli a hőtermelést.

Nem állítom, hogy a 14nm-es zen1 frekvencia skálázódása emiatt állt meg, de amikor a 12nm-re váltottak, akkor a hírekben arra hivatkoztak a fizikai kiterjedés megtartásával kapcsolatban, hogy így több a "hely" a hőt termelő tranzisztorok között és könnyebben hűl

Valamint a zen2 esetén is szó volt róla, hogy nagyon szép és szuper, hogy milyen sűrű a 7nm-es gyártástechnológia, de az intel abból a szempontból könnyebb helyzetben van, hogy a lapkái 2x akkora kiterjedésűek, és ennélfogva engedheti meg magának a ~2x akkora fogyasztást. másként megfogalmazva: a hősűrűség miatt az AMD ha akarná se tudná növelni a fogyasztást.Szerintem a 3D technológia terjedésével ez a probléma fokozódni fog. A rétegződéssel - gondolom valamelyest növekedni fog a lapkák magassága (Az ExecutableFix által megosztott/renderelt Raphael kupak például kifejezetten magasnak tűnik) A legalsó réteg biztosan távolabb kerül a hőelvezetést szolgáló hűtött felső felülettől. Tehát szerintem egyre kevésbé lesz megengedhető, hogy neked valahol a szilícium téglatestedben - főleg alul - legyen valami nagy hőkoncentrációt okozó részegységed.

Vannak elképzelések a 3D stacked chipek Z irányú hűtésére, de azért annál szerintem lényegesen egyszerűbb, ha a hőtermelést a frekvencia csökkentésével oldják meg. a chipek ma már tele vannak hőérzékelőkkel, tehát nem gondolom, hogy bármikor is alattomosan ki tudna alakulni valami hőtermelő központ, ami leégeti a chipet.

A másik fontos szempont ami megjelenik, hogy ha valahol nagy hő képződik, akkor oda a szükséges kakaót is el kell juttatni.Számomra minden szempontból előnyösebbnek tűnik az alacsonyabb feszültség és a frekvencia és a 3D stacking által kínált cache és feldolgozó szélesítési lehetőség.

Az Apple a példa rá, hogy ebben a vonatkozásban jelenleg az Arm tűnik előnyösebb pozícióban levőnek. És arról pedig volt már szó, hogy az x86 esetén az instruction decoder szélessége tűnik jelentős korlátozó tényezőnek a feldolgozók szélesítése kapcsán.

-

S_x96x_S

addikt

válasz

S_x96x_S

#5243

üzenetére

S_x96x_S

#5243

üzenetére

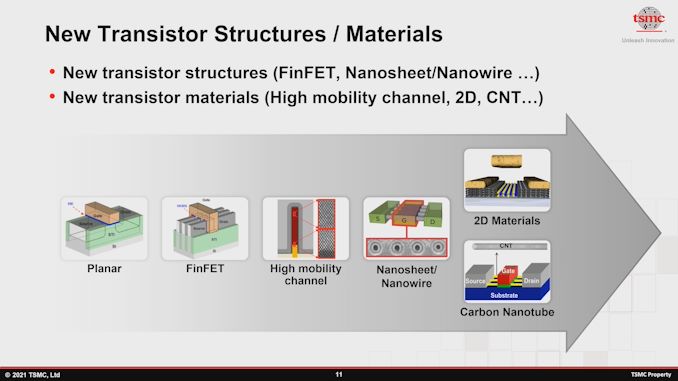

TSMC ..

June 8, 2021

An AnandTech Interview with TSMC: Dr. Kevin Zhang and Dr. Maria MarcedIC: As process nodes shrink, resistance on metal layers is becoming more problematic. With regards innovative solutions, and exotic materials versus copper interconnects, is it just a case of more research down that front? Or do we need to put more effort into increasing and routing higher metal layers?

KZ: I think in the research session at our advanced technology introduction, we did cover a little bit about the back end work. For example, we are continuing to optimize the copper grain boundary to bring a lower resistance metal line to our overall chip technology and new technology. Also, with dielectrics we continue to find innovative materials to improve the dielectric in parasitic capacitance. So, those things are being actively researched.

The 3D integration can also bring an alternative solution to this whole performance requirement in the back-end. You can instead route from A to B in a 2 dimensional space, or you can route A to B vertically in 3 dimensions. In some cases, by going vertical, you can reduce the overall length of the RC wire, and reduce pass delay significantly. So all those things have to be looked at going forward.

Új hozzászólás Aktív témák

- PlayStation 5

- TCL LCD és LED TV-k

- Ring of Elysium (Battle Royale)

- Chieftec-Prohardver nyereményjáték

- Robotporszívók

- Békéscsaba és környéke adok-veszek-beszélgetek

- Arc Raiders

- Bluetooth hangszórók

- Mesébe illő csodakábelt tervezett a GeForce-ok leégése ellen a Segotep?

- Hitelkártyák használata, hitelkártya visszatérítés

- További aktív témák...

- Sony G 24-105 f/4 - Sigma 50mm f/1.4 Art (SONY E)

- Összeszerelésre váró komplett gépezet várja új gazdáját!

- BONTATLAN Új Iphone 17 256GB White -Fe Szín 1év APPLE garancia gyári független Deák AZONNAL Átvehet

- Asus P5a-b Ss7 dobozos alaplap / K6-2+ 500mhz / Voodoo 3 /Awe 64 / Big Box Game

- Eladó 82 colos 4K HDR Samsung TV

- LENOVO Legion Pro 5 16IRX8 - 16" WQXGA 240Hz - i5-13500HX - 16GB - 1TB - RTX 4060 - 9 Hó garancia

- Dell Latitude 7410 Intel I7-10810U Refurbished - Garancia

- BESZÁMÍTÁS! MSI B450 R5 5600X 32GB DDR4 512GB SSD RTX 3080 10GB RAMPAGE Shiva Cooler Master 750W

- Gamer PC-Számítógép! Csere-Beszámítás! I5 14400F / RTX 3060Ti / 32GB DDR5 / 512GB SSD!

- Samsung Galaxy A53 5G 128GB, Kártyafüggetlen, 1 Év Garanciával

Állásajánlatok

Cég: PCMENTOR SZERVIZ KFT.

Város: Budapest

Cég: ATW Internet Kft.

Város: Budapest