Új hozzászólás Aktív témák

-

S_x96x_S

addikt

> Hogy a maradék 4µs hardware latency mire megy el

> az ábrán, az nekem nem világos.valószínüleg a

- PCIe 3.0 ( csak nemrég jelent meg a Gen4 -es Optane SSD )

- és az NVMe protocol overheadje ( a PCIe felett ) lehet.de még ha nem is tökéletes - de ettől függetlenül az ábra arra jó,

hogy jelezze, hogy mennyi optimalizálandó

van még a rendszerben,-----------------

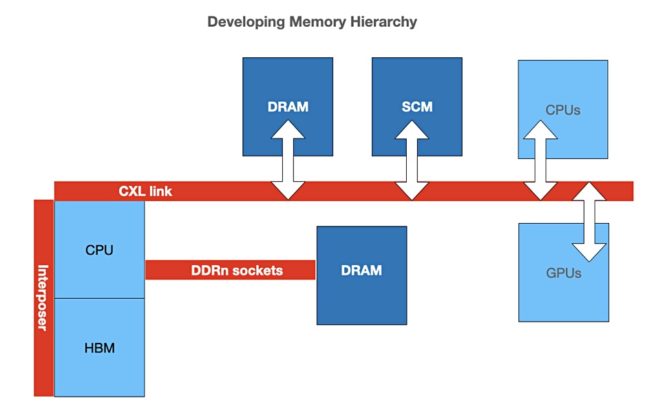

Roland Dreier, a senior staff engineer at Google, has tweeted that “HBM is not a good match for CXL, since even future CXL at gen6 x8 speeds tops out at 100 GB/sec, while HBM2E already goes from 300+ GB/sec to TB/sec speeds.” He suggests the industry could “build CXL “memory drives” from normal DRAM.”

Dreier says: “You could imagine a future memory hierarchy where CPUs have HBM in-package and another tier of CXL-attached RAM, and DDR buses go away. (Intel is already talking about Sapphire Rapids SKUs with HBM, although obviously they still have DDR5 channels.)”

He also sees scope for 3D XPoint with CXL: “a 3DXP drive with a 50 GB/sec low-latency byte-addressable CXL.mem interface seems like a killer product that gives new capabilities without forcing awkward compromises.”

https://blocksandfiles.com/2021/03/25/cxl-and-the-developing-memory-hierarchy/

Új hozzászólás Aktív témák

- Milyen egeret válasszak?

- Milyen TV-t vegyek?

- 5.1, 7.1 és gamer fejhallgatók

- Audi, Cupra, Seat, Skoda, Volkswagen topik

- Bemutatkozott a Poco X7 és X7 Pro

- Windows 11

- Apple Watch Sport - ez is csak egy okosóra

- Külföldi rendelések: boltok, fizetés, postázás

- Telekom mobilszolgáltatások

- AMD GPU-k jövője - amit tudni vélünk

- További aktív témák...

- ROG Strix G732LWS 17.3" FHD IPS i7-10875H RTX 2070 Super 32GB 1TB NVMe gar

- Logitech PRO-X 981-000818 (Bontatlan)

- SteelSeries Arctis Nova Pro Wireless (Bontatlan)

- ZBook Fury 16 G10 16" FHD+ IPS i7-13850HX RTX 3500 Ada 32GB 1TB NVMe ujjlolv IR kam gar

- Samsung Galaxy A53 5G 128GB, Kártyafüggetlen, 1 Év Garanciával

- Lenovo T14 Thinkpad Gen3 WUXGA IPS i5-1245U vPro 10mag 16GB 512GB Intel Iris XE Win11 Pro Garancia

- Bomba ár! HP Revolve 810 G2 - i7-G4 I 12GB I 256GB SSD I 11,6" HD Touch I Cam I W10 I Garancia

- GYÖNYÖRŰ iPhone 13 256GB Midnight -1 ÉV GARANCIA -Kártyafüggetlen, MS3650, 100% Akkumulátor

- Eladó Oppo A78 5G 4/128GB / 12 hó jótállás

- GYÖNYÖRŰ iPhone 12 mini 64GB White -1 ÉV GARANCIA - Kártyafüggetlen, MS3849, 100% Akksi

Állásajánlatok

Cég: ATW Internet Kft.

Város: Budapest

Cég: PCMENTOR SZERVIZ KFT.

Város: Budapest